题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

试用D触发器和与非门实现图时序电路,T为输出Q0、Q1、Q2的变化周期。

试用D触发器和与非门实现图时序电路,T为输出Q0、Q1、Q2的变化周期。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

试用D触发器和与非门实现图时序电路,T为输出Q0、Q1、Q2的变化周期。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试用D触发器和与非门实现图时序电路,T为输出Q0、Q1、Q2…”相关的问题

更多“试用D触发器和与非门实现图时序电路,T为输出Q0、Q1、Q2…”相关的问题

试用PLA和D触发器设计一个具有以下逻辑功能的电路,并画出PLA阵列图。

①当M=0时,D4D3D2D1=ABCD

②当M=1时,D4=Q3、D3=Q2、D2=Q1、D1=0在CP作用下实现左移操作。

图10.18为一个左移位寄存器,在下侧加一个组合逻辑电路(与非门G1,G2,G3和G4)。数码由D端经组合逻辑电路送至最低位触发器输入端 D0。X为控制端。试分析当X=0和X=1时,电路的逻辑功能。

1.jpg)

A.正确

B.错误

在图10.3.7所示TTL与非门构成的单稳态触发器中,若输入v1为宽度20μs的脉冲,试画出vO1、vI2、vO3、vO的波形,计算输出脉冲宽度。为使该电路能正常工作,对输入脉冲有何要求。

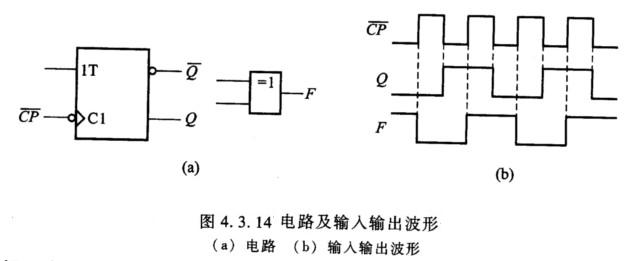

试用图4.3.14(a)给定的触发器和逻辑门设计波形产生电路。要求图(a)中的各信号满足图4.3.14(b)所示时序关系。

在图3-15所示网络中,已知各元件参数为R1=200Ω,R2=500Ω,L=100H,C=1000μF,激励源is=1A。当t=0时闭合开关S,试用状态变量法求电流iL(t)和电压uC(t)。