题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

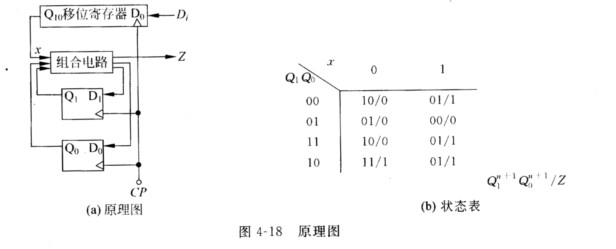

图中电路由一个11位移位寄存器和时序电路构成,移位寄存器寄存信息11000011101且自右向左移位输出串行信号x,

作用到时序电路输入端,再对外输出z。时序电路状态表如图(b),初态00,试作出时序电路状态输出Q1、Q2和外输出z波形图。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图中电路由一个11位移位寄存器和时序电路构成,移位寄存器寄存…”相关的问题

更多“图中电路由一个11位移位寄存器和时序电路构成,移位寄存器寄存…”相关的问题

图4-18电路由一个11位移位寄存器和时序电路构成,移位寄存器寄存信息11 000011101且自右向左移位输出串行信号x,作用到时序电路输入端,再对外输出x。时序电路状态表如图4-18(b),初态00,试作出时序电路状态输出Q1、Q2和外输出z波形图。

一个11位左移移位寄存器和两个同步时序电路相连,如图4-56(a)所示。这两个同步时序电路的状态如图4-56(b)所示。设寄存器的状态为01101000100,两个时序电路均处于00状态,试确定在11个CP脉冲作用下Z2的输出序列。

.jpg)

试设计一个时序电路,将16字×4位的ROM中的数据变为串行码,并自动循环输出。(建议:用555,'161和'194等实现。)

图10.18为一个左移位寄存器,在下侧加一个组合逻辑电路(与非门G1,G2,G3和G4)。数码由D端经组合逻辑电路送至最低位触发器输入端 D0。X为控制端。试分析当X=0和X=1时,电路的逻辑功能。

按如图所示波形要求,设计一个同步时序电路,对空闲不用状态可视为任意项,以保证电路结构最简。(要求选用JK触发器)