更多“4位二进制计数器有8个计数状态。()”相关的问题

更多“4位二进制计数器有8个计数状态。()”相关的问题

第7题

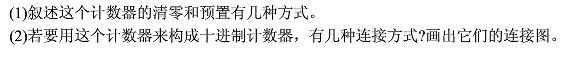

74ALS561是一种功能较为齐全的同步计数器。其内部是4位二进制计数器。功能表和引脚示意图如图所示(QD为高位输

74ALS561是一种功能较为齐全的同步计数器。其内部是4位二进制计数器。功能表和引脚示意图如图所示(QD为高位输出)。其中 为输出高阻控制端,OOC是与时钟同步的进位输出,其他各输入、输出端的功能可由功能表得知。

为输出高阻控制端,OOC是与时钟同步的进位输出,其他各输入、输出端的功能可由功能表得知。

第10题

若要实现一个可暂停的一位二进制计数器,控制信号A=0计数,A=1保持,可选用T触发器,且令T=A。()

若要实现一个可暂停的一位二进制计数器,控制信号A=0计数,A=1保持,可选用T触发器,且令T=A。()

点击查看答案

A.正确

B.错误

第11题

如图所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1M

如图所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

如果结果不匹配,请

如果结果不匹配,请