题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

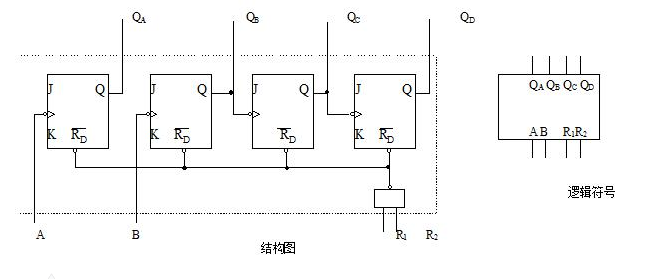

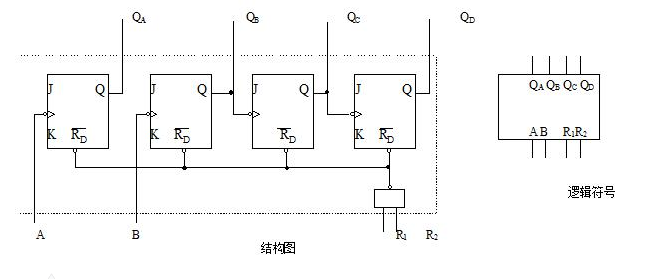

已知某集成计数器的结构图及逻辑符号如图所示,虚线以内为集成电路的内部电路。要求: (1)单片计数器能实现

已知某集成计数器的结构图及逻辑符号如图所示,虚线以内为集成电路的内部电路。要求:

(1)单片计数器能实现的最大模值为多少;

(1)单片计数器能实现的最大模值为多少;

(2)画出用该计数器实现五进制计数器的逻辑图;

(3)画出用该计数器实现六进制计数器的逻辑图;

(4)画出用该计数器实现三十进制计数器的逻辑图。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知某集成计数器的结构图及逻辑符号如图所示,虚线以内为集成电路的内部电路。要求:

(1)单片计数器能实现的最大模值为多少;

(1)单片计数器能实现的最大模值为多少;

(2)画出用该计数器实现五进制计数器的逻辑图;

(3)画出用该计数器实现六进制计数器的逻辑图;

(4)画出用该计数器实现三十进制计数器的逻辑图。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“已知某集成计数器的结构图及逻辑符号如图所示,虚线以内为集成电…”相关的问题

更多“已知某集成计数器的结构图及逻辑符号如图所示,虚线以内为集成电…”相关的问题

1.jpg)

集成DAC器件AD7520电路如图题8.6所示,其应用电路如图题8.9所示。已知AD7520参数:电源电压为+5V~+15V,分辨率为10位,稳定时间为500ns。为得到±5V的最大输出模拟电压,试确定基准电压VREF、偏移电压VB及偏移电阻RB,并列出高三位(含符号位)输入输出对照表。

某随动系统,忽略小时间常数,采用并联校正,其简化的结构图如图5所示,其中

1)求出Wc(s)传递函数的形式与参数。

2)求出满足该指标的Kobj值。

3)画出用并联校正时的系统对数幅频特性。

TTL集成施密特触发器CTll32的逻辑符号和vI一vO曲线如图9.6.1(a)所示,图(b)为CTll32组成的电路。 (1)说明电路具有什么功能。 (2)定性画出VA,VO的波形。 (3)若R=10 kΩ,C=0.01μF,计算工作周期。

.jpg)

写出如图52集成译码器T4139输出

某同学用图(a)所给器件构成电路,并在示波器上观察到如图(b)所示波形。试问电路是如何连接的?请画出逻辑电路图,并标明T值。

如图8—6所示,轴是固定的,工作条件要求A0=5.0-5.2mm,已知:

用理想集成运放组成的对数变换器如图6-11所示,已知VCC=10V,R6=1MΩ,R1=10kΩ,(R3+R4)/R3=16.8。设各管特性相同,β足够大,试在室温时,

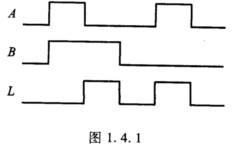

已知逻辑函数L的波形图如图1.4.1所示,则逻辑函数满足()。

A.L=A⊙B

B.

C.L=A+B

D.L=AB