题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

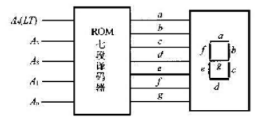

题图所示是用ROM构成的七段译码电路框图。A4~A0是ROM的输入端,其中A3~A0,是数据输入端,最高位A4只用作试灯输

题图所示是用ROM构成的七段译码电路框图。A4~A0是ROM的输入端,其中A3~A0,是数据输入端,最高位A4只用作试灯输入端(LT)。当 LT=1时,不论二进制数码A3A2A1A0为何值,数码管七段全亮,当LT=0时,数码管则显示4位二进制数所对应的十进制数码。半导体数码管为共阴极接法。试列出实现上述逻辑要求的ROM功能表,并画出ROM的阵列图。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“题图所示是用ROM构成的七段译码电路框图。A4~A0是ROM…”相关的问题

更多“题图所示是用ROM构成的七段译码电路框图。A4~A0是ROM…”相关的问题

。

。

1.jpg)